低功耗带隙基准电压源电路设计

- 高端制造

- 2024-11-16 07:15:43

- 113

蒋本福(吉林大学珠海学院,广东珠海519000):文章提出一种三层self-cascode管子工作在亚阈值区的低功耗带隙基准电压源电路。该电路具有电路结构简单、功耗低、温度系数小、线性度小和面积小等特......

蒋本福

(吉林大学珠海学院,广东珠海519000)

:文章提出一种三层self-cascode管子工作在亚阈值区的低功耗带隙基准电压源电路。该电路具有电路结构简单、功耗低、温度系数小、线性度小和面积小等特点。采用μm的标准CMOS工艺,华大九天Aether软件验证平台进行仿真。仿真结果表明,在tt工艺角下电路的启动时间为6.64μs,稳定输出的基准电压Vref为567mV;当温度在-40℃~125℃范围内时,tt工艺角下基准电压Vref的温度系数TC为18.8ppm/℃;电源电压在1.2V~1.8V范围内时,tt工艺角下基准电压Vref的线性度为2620ppm/V;在10Hz~1kHz带宽范围内,tt工艺角下基准电压Vref的电源抑制比(PSRR)为51dB;版图核心面积为0.00195mm2。

:Aether软件;功耗;温度系数;线性度;面积

:TN432文献标识码:ADOI:10.19358/

引用格式:蒋本福.低功耗带隙基准电压源电路设计[J].微型机与应用,2017,36(3):39-41.

0引言

在模拟IC和混合IC中,带隙基准电压是不可缺少的电路模块。传统的低压、低功耗带隙基准电路是基于垂直双极晶体管,在文献[12]中分别提出了多种设计方法。然而,这些方法都需要几百兆欧姆的电阻实现低功耗运行,占用较大芯片面积,浪费资源。参考文献[3]也提出了由几个工作在亚阈值区的MOS管组成的电路,虽然保证了低功耗,但是也出现了温度补偿不够等问题。为了实现低温漂带隙基准电压电路,高阶温度补偿技术[5]必须得到广泛应用,以减小带隙电压的温度系数。因此本文提出在低功耗的带隙基准基础上增加高阶温度补偿电路来实现低温漂基准电压电路。

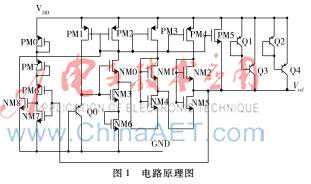

1电路结构分析

其中VDSN为NMOS的漏源电压,VGSN为NMOS的栅源电压,VE为BJT的发射极基极电压,S为MOS管的宽长比比值,ΦT为热电压,n为亚阈值系数。

由于BJT的发射极基极电压VE具有高阶的温度系数,因此采用图1Q1Q3和Q2Q4部分构造指数型补偿电路[5]。其中流经Q3、Q4的集电极电流是一个与温度成高阶温度关系的量,把这一电流引入带隙基准源的输出端可以对带隙基准源进行高阶的温度补偿。

2电路仿真结果

仿真采用μm的标准CMOS工艺,华大九天Aether软件验证平台,各种仿真与分析如下。

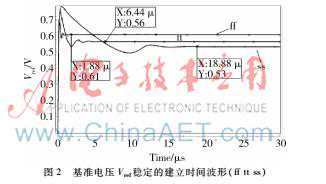

2.1不同工艺角下的启动电路仿真与分析

瞬态仿真,可得到基准电压Vref稳定的建立时间,如图2所示。

由图2可知,电路在不同工艺角下的启动时间相差不大。

2.2不同工艺角下的电路功耗仿真与分析

如图3所示,各工艺角下电路的总电流分别为:μA,,。

由于在不同的工艺角下,MOS管具有不同的阈值电压,BJT具有不同的导通电压,使得在ff工艺角下部分工作在亚阈值区的管子进入饱和区,从而增大了基准电流,其中在ss工艺角下所有的电流镜管子均进入亚阈值区。

因此,在不同工艺角下电路的总电流出现不同的变化,相应地也会对温度系数产生一定的影响。

2.3不同工艺角下的电路温度特性曲线仿真与分析

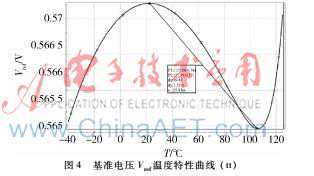

2.3.1基准电压Vref温度特性曲线仿真与分析

基准电压Vref的温度特性曲线如图4所示,具体仿真结果与分析如下:

(1)温度在-40℃~125℃范围内时,tt工艺角下基准电压Vref的温度系数为18.8ppm/℃;

(2)温度在20℃~50℃范围内时,tt工艺角下基准电压Vref的温度系数为4.0ppm/℃。

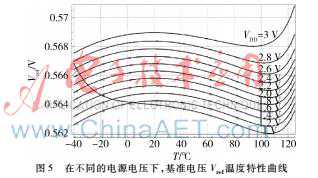

2.3.2在不同的电源电压下基准电压Vref温度特性曲线

如图5所示,电源电压在1V~3V范围内,参数扫描具体仿真结果与分析如下:当电源电压为1.2V~2.8V时,在-40℃~125℃温度范围内,tt工艺角下基准电压Vref的温度系数TC在18~21ppm/℃之间。

2.4不同工艺角下的基准电压的线性度仿真与分析

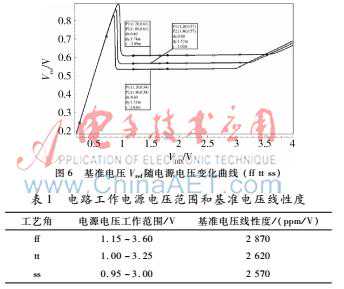

图6所示为在0.2V~4V电源电压内,3个工艺角的基准电压Vref随电源电压变化曲线。

具体仿真结果与分析如表1所示。表1电路工作电源电压范围和基准电压线性度工艺角电源电压工作范围/V基准电压线性度/(ppm/V)~3.602870~3.252620~3.002570

2.5不同工艺角下的电路电源抑制比仿真与分析

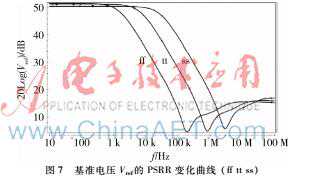

如图7所示,频率在低频范围内,3个工艺角下基准电压Vref的PSRR均大于50dB。

具体仿真结果与分析如表2、表3所示。表2不同工艺角下由表2、表3可知,在10Hz~1kHz范围内,基准电压Vref在3个工艺角下的PSRR均在-51dB左右。

由图7可知,当频率为10kHz时,在ff和tt工艺角下基准电压Vref仍具有-50dB和-49dB的PSRR。3版图设计

版图的整体设计如图8所示。

4结论

本文设计了一款基于温度补偿的CMOS低压、低功耗的带隙基准电压源。利用MOS管工作在亚阈值区域过驱动电压低、饱和电流小的特性,能够实现在输入较低的电源电压范围内,功耗降低到nW级带隙基准电路设计。同时,在输出级增加温度补偿电路,提高电路的温度补偿能力。本电路还有电路结构简单、功耗低、线性度好、温度系数小、PSRR较好、芯片面积小等特点。

参考文献

[1]UENOK,HIROSET,ASAIT,,15ppm/℃,20ppm/vcmosvoltagereferencecircuitconsistingofsubthresholdmosfets[J].SolidStateCircuits,IEEEJournalof,2009,44(7):20472054.

[2]LiYongquan,/℃temperatutrecoefficient[C].ICCEIW,2015.

[3]陈新弼,张庆中,陈勇.微电子器件[M].北京:电子工业出版社,2011.

[4]SAINTC,SAINTJ.集成电路掩膜设计[M].周润德,金申美,译.北京:清华大学出版社,2006.

[5]AlanHastings.模拟电路版图的艺术(第二版)[M].张为,等译.北京:电子工业出版社,2011.

本文链接:https://goko.jsntrg.cn/519651853493.html